微机原理与接口技术(六)

输入输出技术概述

- I/O接口的基本功能

- I/O接口及其编址方式

- I/O地址编码

1.I/O接口

- 接口要解决的问题

- 速度匹配→数据的缓冲与暂存

- 信号的驱动能力→信号驱动

- 信号形式和电平的匹配→信号类型转换

- 信息格式→信号格式转换

- 时序匹配(定时关系)

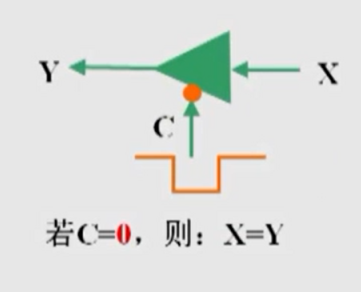

- 总线隔离→三态门

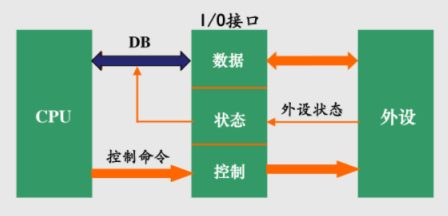

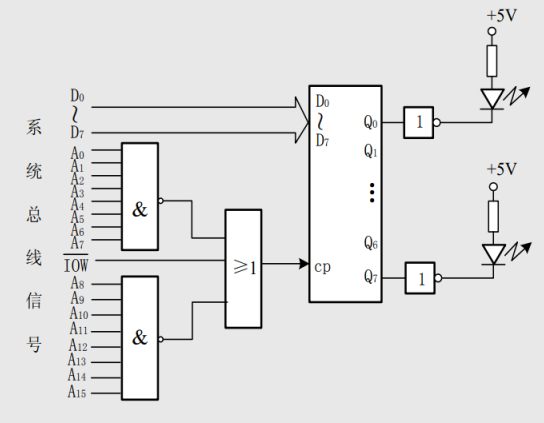

接口的基本构成

见图104

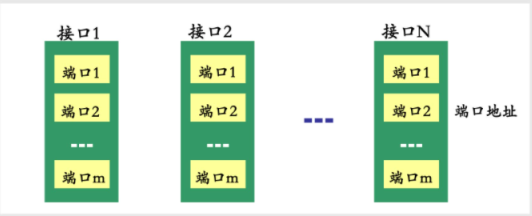

2.I/O端口及其编址

端口:接口电路中用于缓存数据及控制信息的部件

- 数据端口、状态端口、控制端口

见图105

![105]()

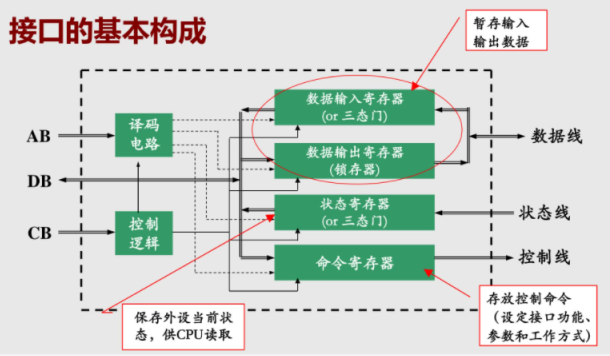

I/O端口编址

计算机系统中包含各类不同功能的接口电路

每个接口中含1个或多个端口

见图106

![106]()

端口编址

- 为确保CPU能够访问到每个不同的端口

寻址端口的方法

先找到端口的接口电路芯片→片选

再在该芯片上找具体访问的端口→片内寻址

若接口中仅有一个端口,则找到芯片即找到端口

若接口中由多个端口,则找到芯片后再找端口

每个端口地址=片选地址(高位地址)+片内地址

8086/8088寻址端口的能力

- 64K个端口

端口的编址方式

- 与内存统一编址

- 独立编址

- 内存地址资源充分利用,能够应用于端口的指令较少

见图107

8088/8086的I/O端口编址

- 采用I/O独立编址方式,与内存共用地址总线,用IO/#M信号状态区分

- 访问端口时仅使用地址总线的:A15~A0

- 可寻址的I/O端口为64K(65536)个,I/O地址范围:0~FFFFH

- IBMPC只使用了1024个I/O地址(0~3FFH)

3.I/O地址译码

目的:

- 确定端口的地址

参加译码的信号

- #IOR,#IOW,高位地址信号

对端口读/写信号的产生条件

- IO/#M=1

- #RD=0→#IOR=0

- #WR=0→#IOW=0

OUT指令将使总线的#IOW信号有效

IN指令将使总线的#IOR信号有效

当接口只有一个端口时

- 无片内地址,全部地址信号均为高位地址(可全部参与译码),译码输出直接选择该端口

当接口具有多个端口时

- 则16位地址线的高位参与译码(决定接口的基地址),而低位则用于确定要访问哪一个端口

由于端口资源丰富,端口地址译码常采用部分地址译码

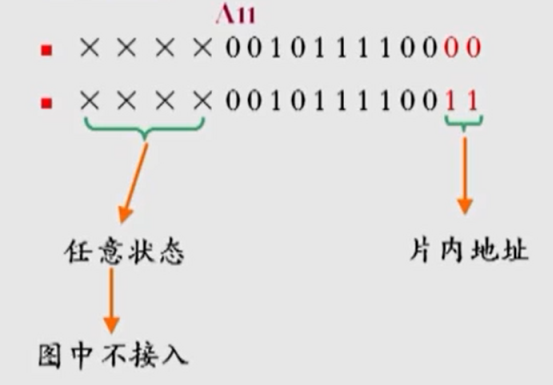

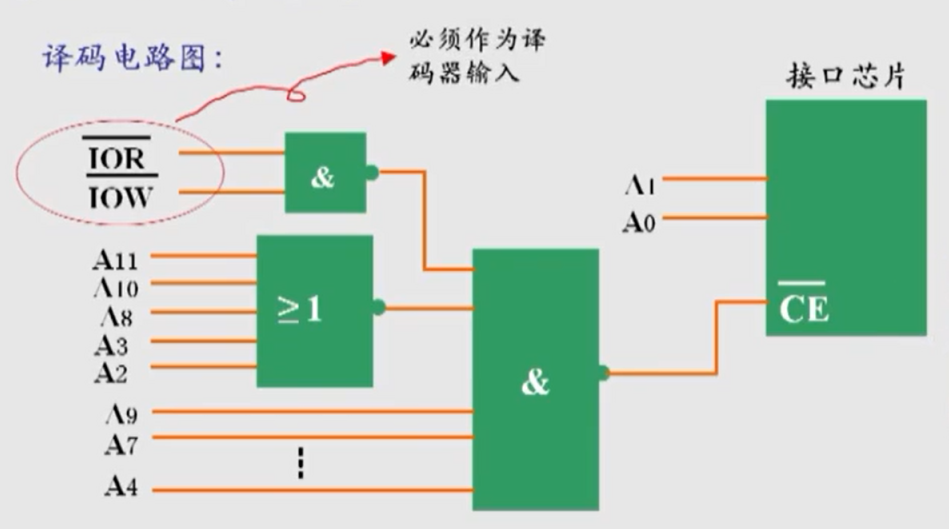

I/O地址译码例

某外设接口有4个端口,地址为2F0H——2F3H,由A15~A2译码得到,而A1,A0用来区分接口中的4个端口。试画该接口与系统的连接图

地址范围

见图108

![108]()

译码电路图

见图109

![109]()

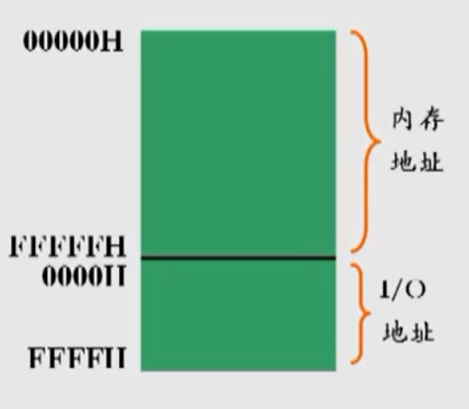

简单接口电路

1.接口的分类及特点

- 按传输信息的方向分类:

- 输入接口

- 输出接口

- 按传输信息的类型分类:

- 数字接口

- 模拟接口

- 按传输信息的方式分类:

- 并行接口

- 串行接口

见图110

接口特点

输入接口

要求对数据具有控制能力

常用三态门实现

见图111

![111]()

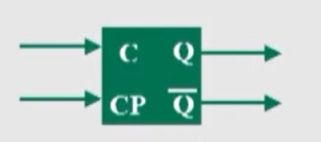

输出接口

要求对数据具有锁存能力

常用锁存器实现

见图112

![112]()

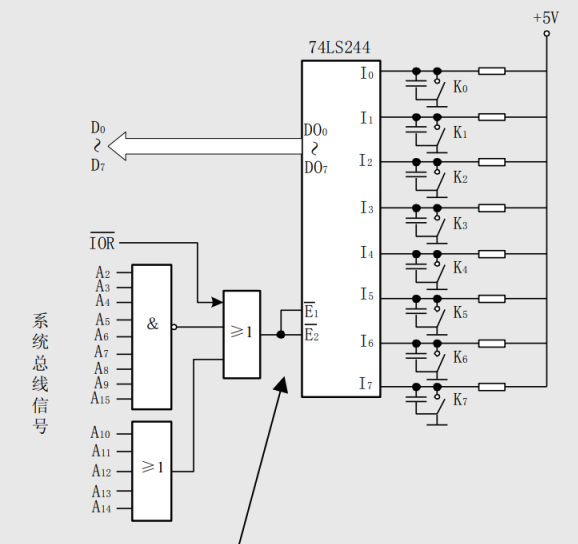

2.三态门接口

- 特点:

- 具有对数据的控制能力,但不具备对数据的控制能力

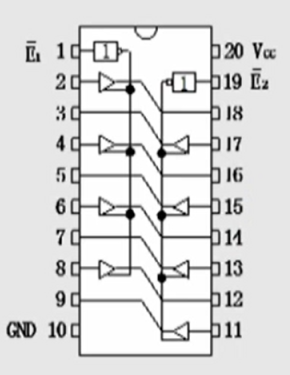

- 74LS244

- 含8个三态门的集成电路芯片

- 在外设具有数据保持能力时用来输入接口

见图113

三态门接口应用例

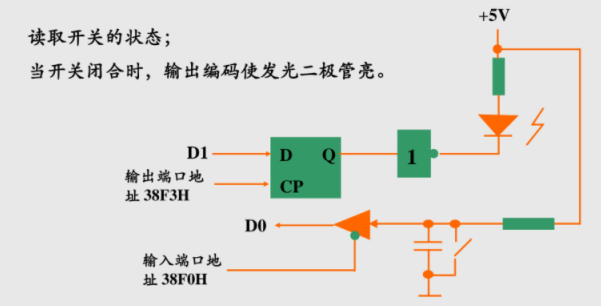

编写程序

判断图中的开关状态。若所有开关都闭合,则程序转向标号NEXT1,否则转向标号为NEXT2的程序执行。

见图114

![114]()

采用看部分地址译码,地址线A1和A0未参加译码

接口芯片的地址范围:

83FCH~83FFH

当地址总线上A15~A0出现此4个地址之一时,#E1#E2端有效,三态门导通。

题目分析

- 当开关断开时,三态门输入端I呈现高电位

- 当开关闭合时,三态门输入端I呈现低电位

1 | MOV DX, 83FCH |

3.锁存器接口

- 特点

- 具有对数据的锁存能力

- 8D锁存器

- 74LS273:8D触发器,不具备数据的控制能力

- 74LS373:含三态的8D触发器,具有对数据的控制能力

- 既可以做输入接口,也可做输出接口

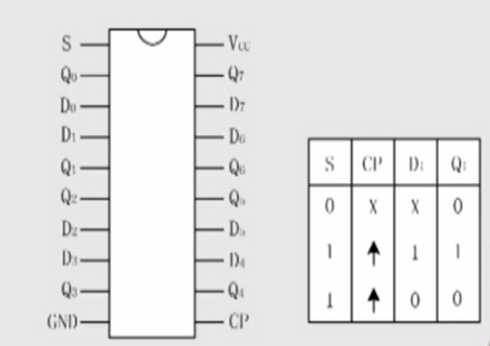

74LS273

由8个D触发器组成

见图115

![115]()

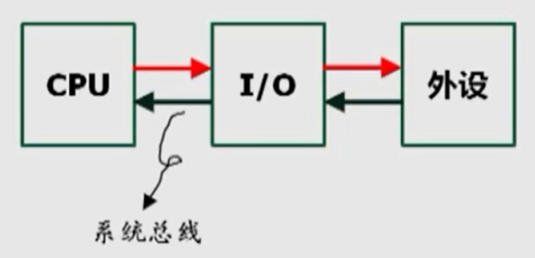

锁存器接口例

应用74LS273作为输出接口,实现对8个发光二极管的控制

见图116

![116]()

题目分析:

- 由图得,要使接到Q端得发光二极管亮,其对应得Q端须输出“1”状态,反之输出“0”状态。

由图得出锁存器74LS273得端口地址:FFFFH

程序段

1

2

3MOV DX, 0FFFFH ;数字得第一个数符是字符型时其前要加0

MOV AL, 01000001B

OUT DX, AL基本输入/输出方法

无条件传送 (程序控制方式)

查询式传送 (程序控制方式)

中断方式传送

直接存储器存取(DMA)

1.无条件传送

- 要求外设总是处于准备好状态

- 优点

- 软件及接口硬件简单

- 缺点

- 只适于简单外设,适应范围较窄

无条件传送例

见图117

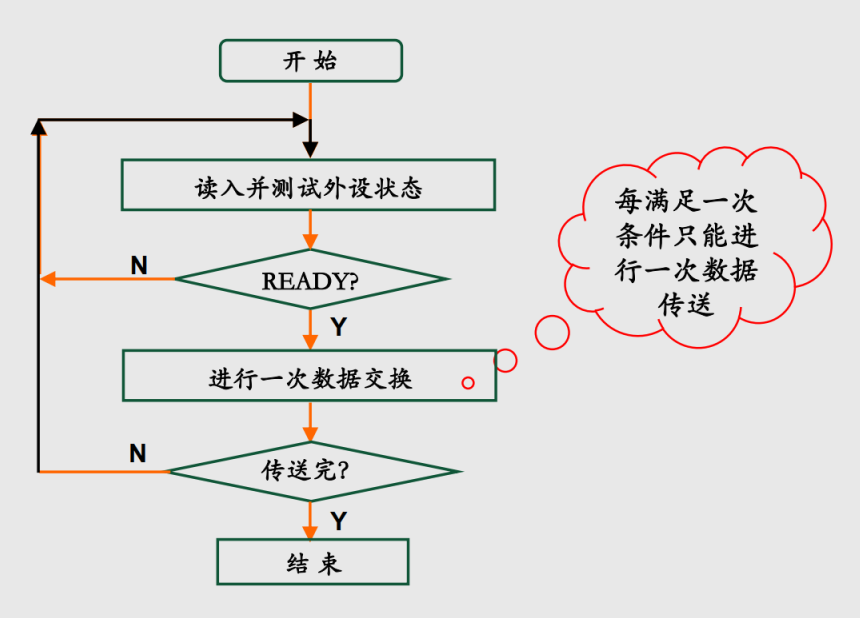

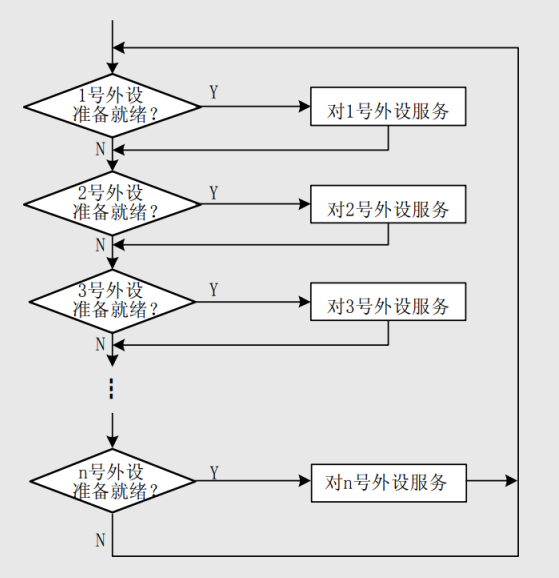

2.查询工作方式

- 仅当条件满足时才能进行数据传送

- 每满足一次条件只能进行一次数据传送

- 适用场合

- 外设并不总是准备好

- 对传送速率和效率要求不高

- 工作条件

- 外设应提供设备状态信息

- 接口应具备状态端口

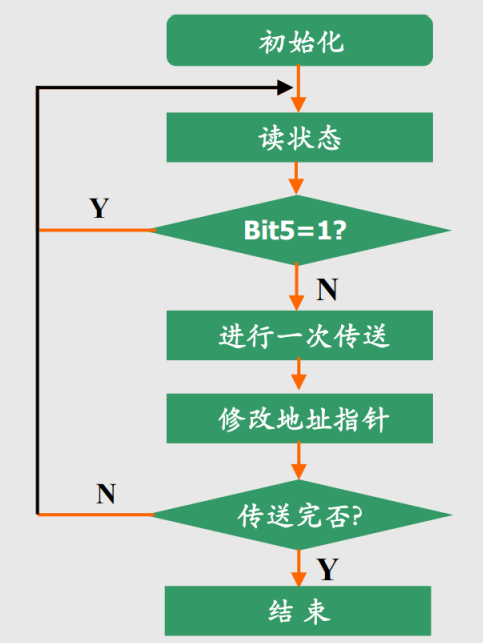

查询工作方式流程图

见图118

- 优点

- 软硬件比较简单

- 缺点

- CPU效率低,数据传送得实时性差,速度较慢

见图119

3.中断控制方式

- 特点:

- 外设在需要时向CPU提出请求,CPU再去为它服务。服务结束后或在外设不需要时,CPU可执行自己的程序

- 优点

- CPU效率高,实时性好,速度快

- 缺点

- 程序编制相对较为复杂

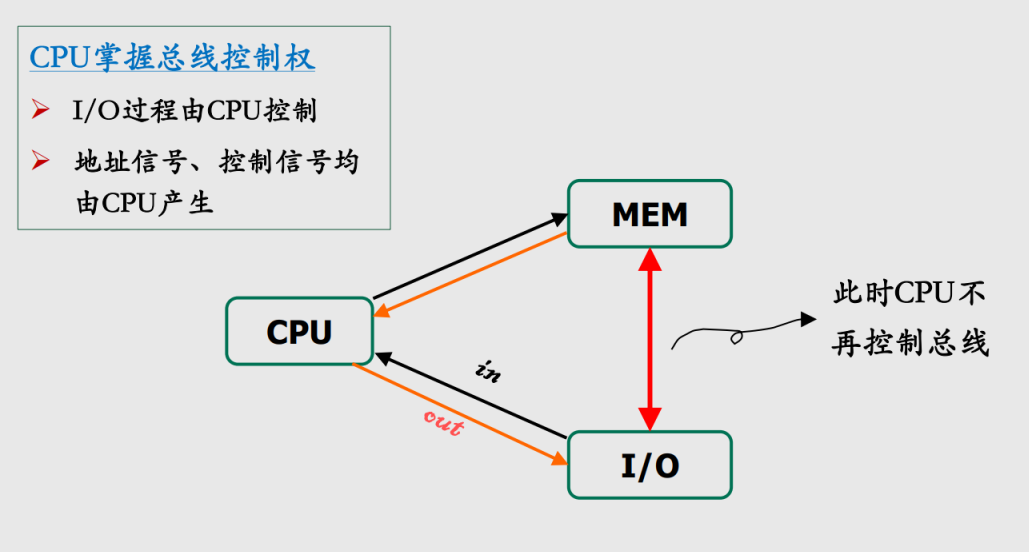

以上三种I/O方式的共性

- 信息传送均需通过CPU

- 软件:

- 外设与内存之间的数据传送是通过CPU执行程序来完成的(PIO方式)

- 硬件:

- I/O接口和存储器的读写控制信号、地址信号都是由CPU发出的

- 缺点:

- 程序的执行速度限定了传送的最大速度

见图120

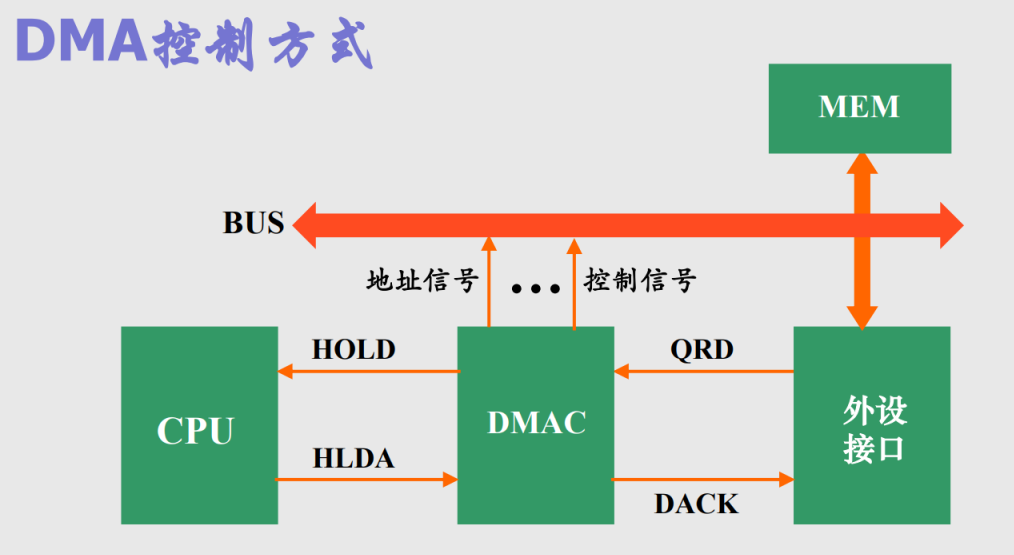

4.DMA控制方式

- 特点:

- 外设直接与存储器进行数据交换 ,CPU不再担当数据传输的中介者

- 总线由DMA控制器 (DMAC) 进行控制 (CPU要放弃总线控制权) ,内存/外设的地址和读写控制信号均由DMAC提供。

见图121

DMA控制方式的工作流程

① 外设向DMA控制器发出“DMA传送请求”信号DRQ

② DMA控制器收到请求后,向CPU发出“总线请求”信号 HOLD;

③ CPU在完成当前总线周期后会立即发出HLDA信号,对 HOLD信号进行响应;

④ DMA控制器收到HLDA信号后,就开始控制总线,并向外设 发出DMA响应信号DACK。

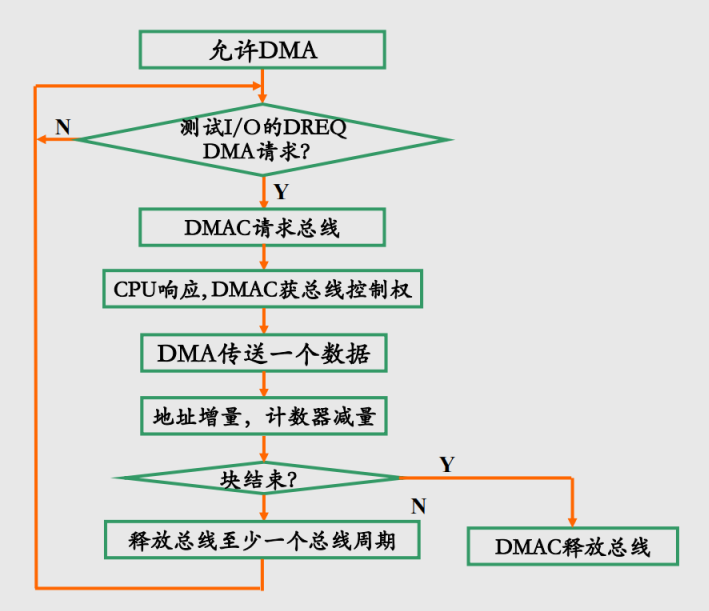

DMA工作方式

周期窃取:

- 每个DMA周期只传送一个字节或一个字就立即释放总线。

数据块传送:

- DMAC在申请到总线后,将一块数据传送完后才释放总 线,而不管中间DREQ是否有效。

直接存取方式:

- DMA的数据传送请求直接发到主存储器,在得到响应后, 整个工作过程在DMA控制器中由硬件完成。

周期窃取的DMA方式

见图122

4种基本I/O控制方式总结

无条件传送:

- 简单,适用范围小,仅适用于“随时准备好”的低速外设

查询工作方式

- 简单,适用于具备“状态信息”的低速外设

- CPU效率低,控制实时性差

中断方式

- 适用于中速外设

- 相对于查询方式,CPU效率较高,控制实时性较好

DMA方式

- 数据传输由DMA硬件来控制,数据直接在内存和外设之间交换,可以达到很高的传输速率。

- 控制复杂,硬件成本相对较高。

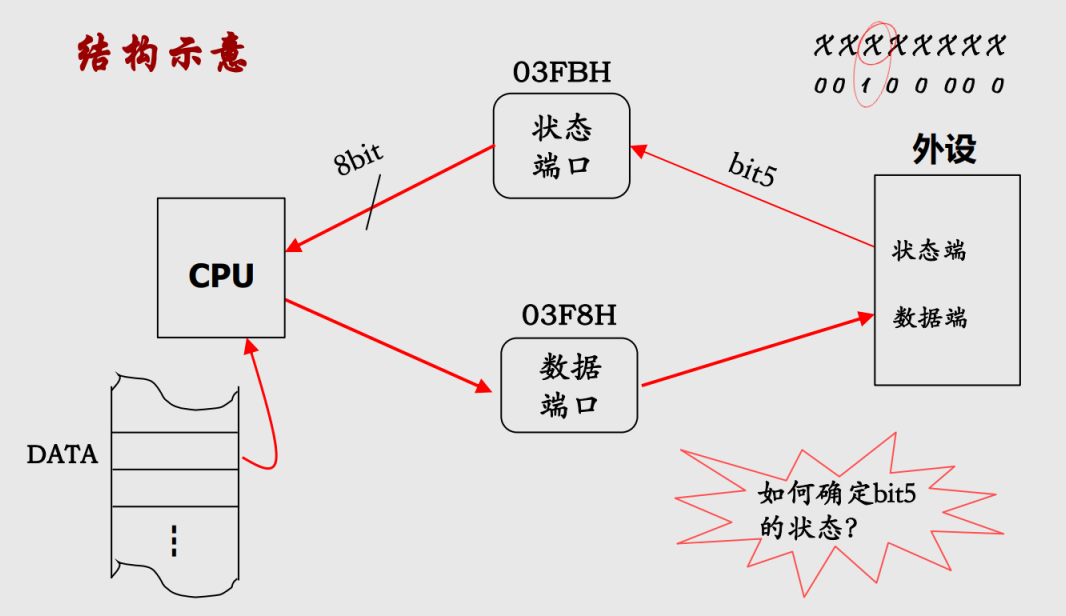

简单I/O控制系统设计

例1

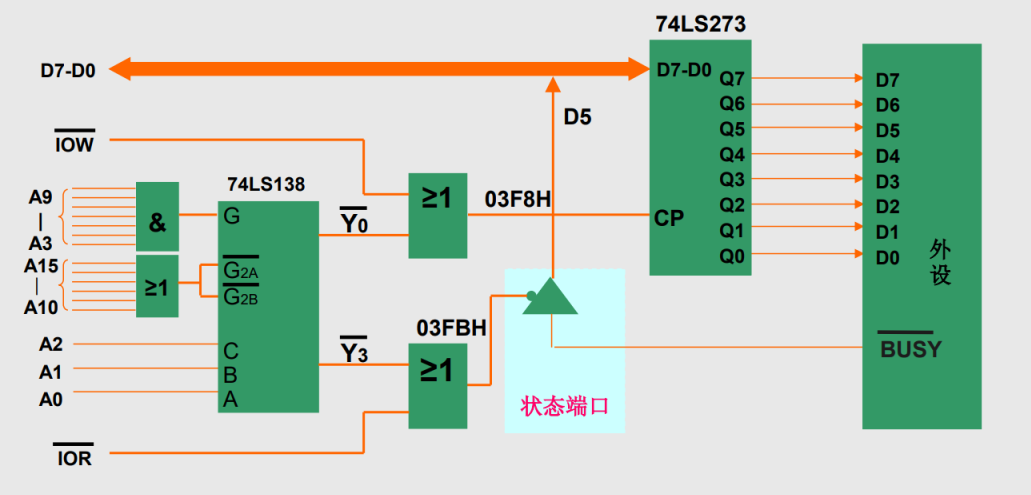

外设状态端口地址为03FBH,第5位(bit5)为状态标志(=1忙,=0准备好);外设数据端口地址为03F8H,写入数据会使状态标志置1;外设把数据读走后又把它置0。

要求:

- 画出该控制系统电路图

- 利用查询工作方式,将DATA下100B数据输出。

见图123

题目分析

- 外设有1位状态位,需要通过输入接口将状态信息输入系统;

- 可选择一个三态门或74LS244接口

- 数据需由系统输出,需要通过输出接口

- 可选择74LS273接口

- 输入接口地址= 03FBH,bit5=1表示“忙”

- 输出接口地址=03F8H

- 待输出数据在内存中的首地址=DATA;

- 待输出数据块大小=100B

- 外设有1位状态位,需要通过输入接口将状态信息输入系统;

状态端口地址:0000 0011 1111 1011

数据端口地址:0000 0011 1111 1000

见图124

控制程序

1

2

3

4

5

6

7

8

9

10

11

12LEA SI, DATA

MOV CX, 100

AGAIN: MOCDX, 03FBH

WAITT: IN AL,DX

TEST AL, 20H

JNZ WAITT

MOV DX, 03F8H

MOV AL, [SI]

OUT DX, AL

INC SI

LOOP AGAIN

HLT见图125

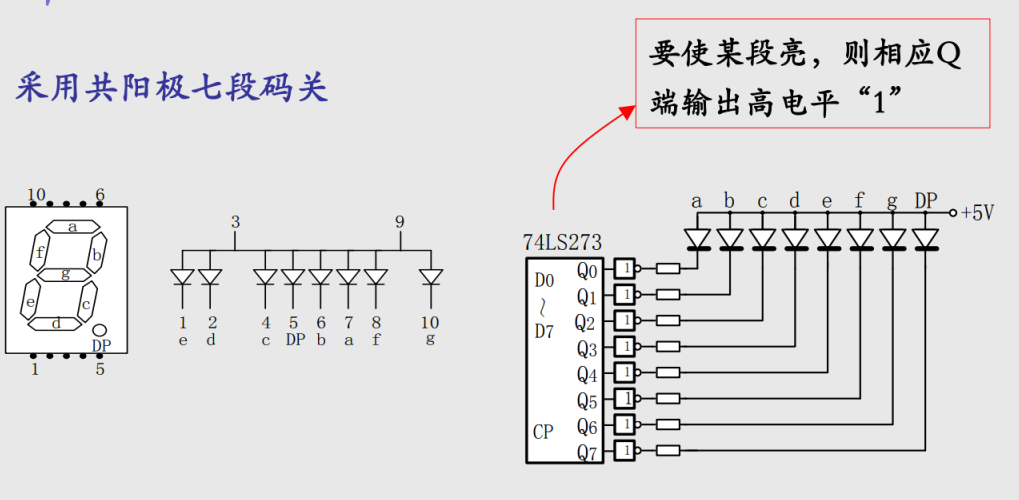

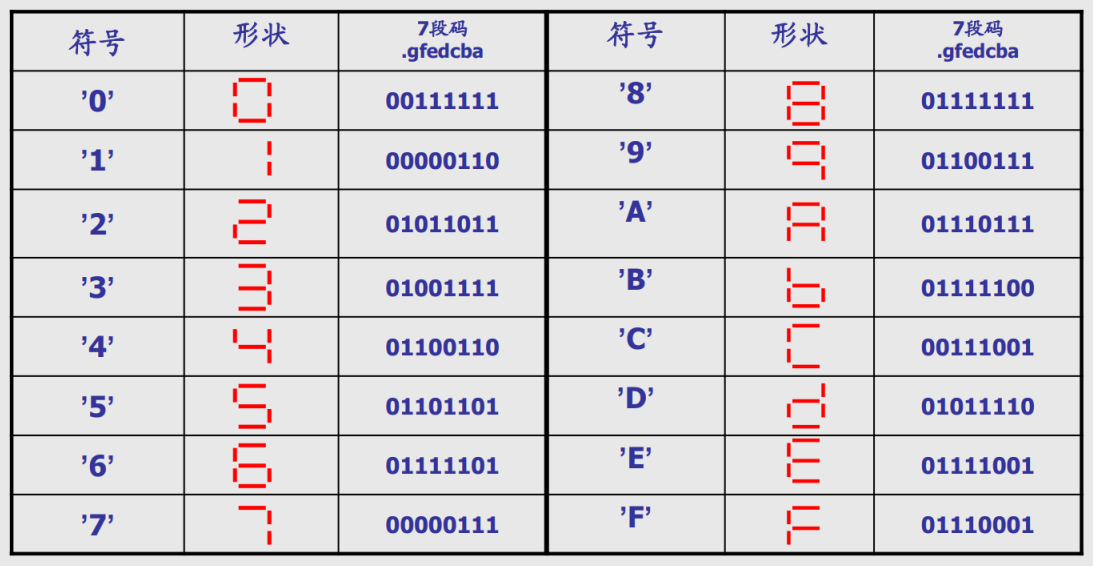

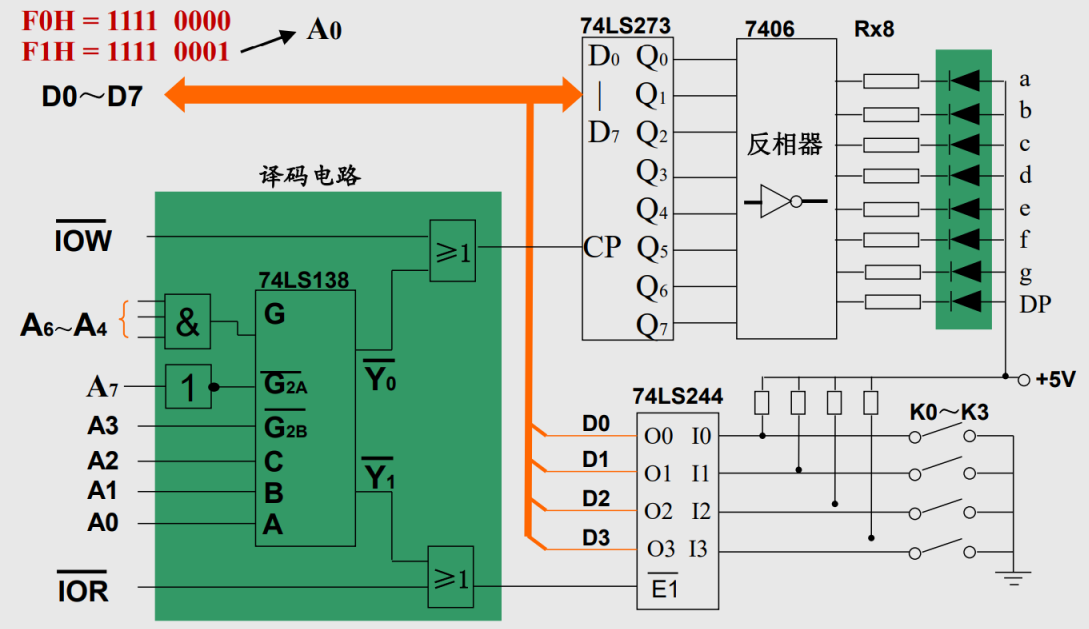

例2

根据开关状态在7段数码管上显示数字或符号

- 设输出接口的地址为F0H,输入接口地址为F1H(仅给出8位地址,为部分地址译码)

- 当开关的状态分别为0000~1111时,在7段数码管上对应显示’0’~’F’

- 外部设备,需要通过I/O接口与系统连接

- 题目分析

- 输入设备:4个开关

- 输出设备:1个七段数码管

- 需要1个输入接口,1个输出接口

见图126

见图127

见图128

- 程序段

见图129

中断技术

- 中断的基本概念

- 中断相应的一般过程

- 中断向量表

- 8088/8086中断系统

1.中断的基本概念

- 中断:

- CPU执行程序时,由于发生了某种随机的事件(外部或内部), 引起CPU暂时中断正在运行的程序,转去执行一段特殊的服务 程序,以处理该事件,该事件处理完后又返回被中断的程序 继续执行,这一过程称为中断。

- 事件为中断源

- 一段特殊的服务程序是中断服务(处理)子程序

- CPU执行程序时,由于发生了某种随机的事件(外部或内部), 引起CPU暂时中断正在运行的程序,转去执行一段特殊的服务 程序,以处理该事件,该事件处理完后又返回被中断的程序 继续执行,这一过程称为中断。

引入中断的原因

- 提高对外设的相应实时性

- 提高了CPU的利用率

- 避免了CPU不断检测外设状态的过程

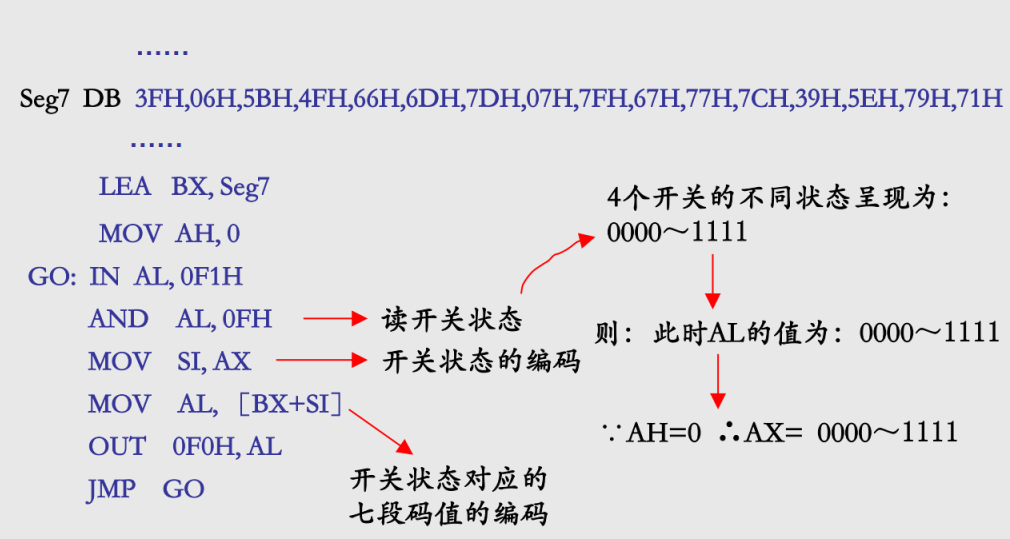

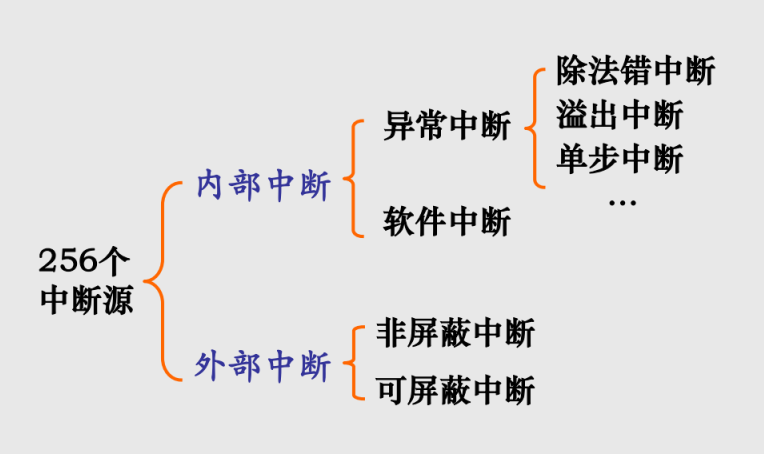

中断类型

- 根据中断请求的来源分为:

- 内部中断

- 异常中断——异常事件引起

- 软件中断——中断指令引起

- 外部中断

- 可屏蔽中断——INTR中断

- 非屏蔽中断——NMI中断

- 内部中断

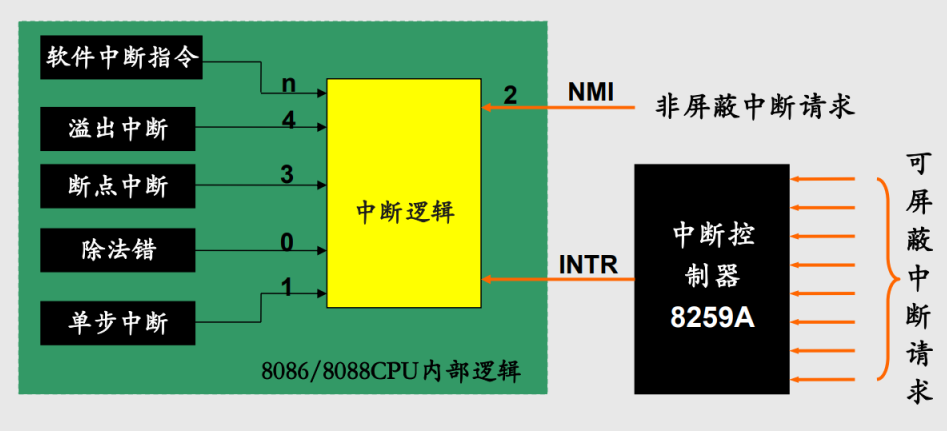

2.外部可屏蔽中断相应的一般过程

- 中断请求

- 中断源识别及中断判优

- 中断响应

- 中断处理(服务)

- 中断返回

1)中断请求

外部可屏蔽中断请求信号:INTR

- 中断请求信号应保持到中断被处理为止;

- CPU响应中断后,中断请求信号应及时撤销。

2)中断源识别

- 软件查询法

- 中断矢量法 → 由中断源提供中断类型号,CPU根据类型确定中断源

中断判优

中断源识别及判优由硬件系统完成

优先级法则

- 低优先级的中断程序允许被高优先 级的中断源所中断

排队法则

- 先来先响应

中断控制器判优:根据中断向量码(中断类型码)确定中断源

见图130

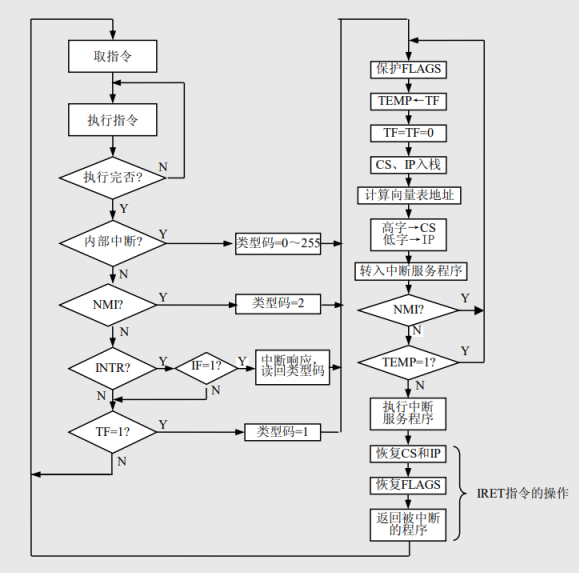

3)中断响应

外部可屏蔽中断响应信号:#INTA

- 向中断源发出#INTA中断响应信号;

- 关中断 → 不允许响应其它中断

- 保护硬件现场 → 将FLAGS压入堆栈

- 获得中断服务程序入口地址

- 以上由硬件系统完成

4)中断处理

- 执行中断服务子程序

- 中断服务子程序的特点:

- 为“远过程”

- 用IRET指令返回

中断服务子程序完成的工作

- 关中断,保护现场,保护断点,找入口地址

- 保护软件现场(参数)

- 开中断(STI)

- 中断处理

- 关中断(CLI)

- 恢复现场

- 中断返回

5)中断返回

- 执行IRET指令,使IP、CS和FLAGS从堆栈弹出

- 恢复断点和硬件现场

中断处理过程

见图131

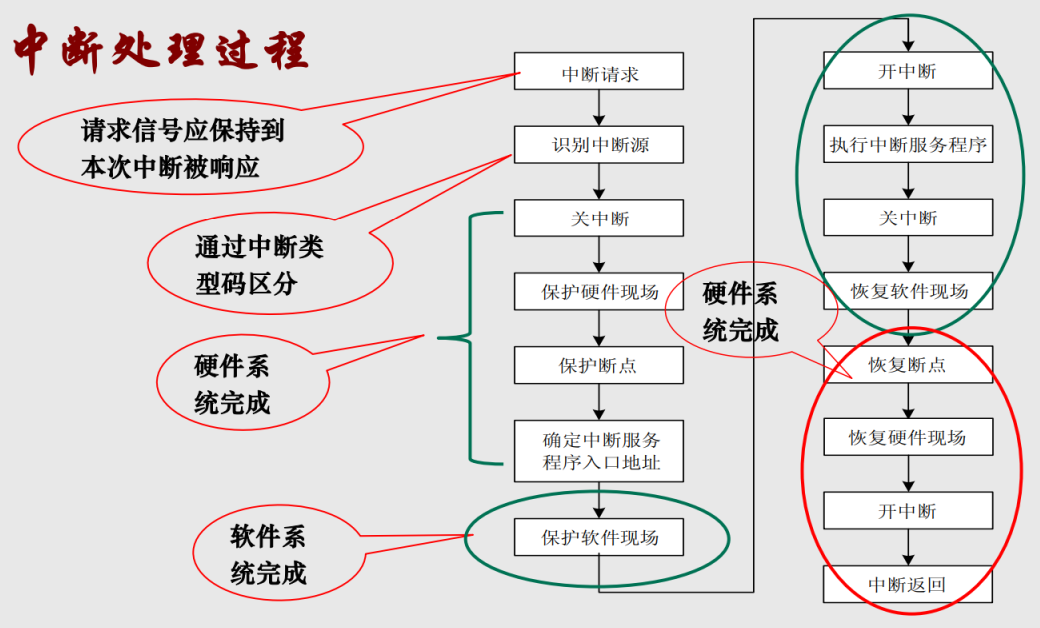

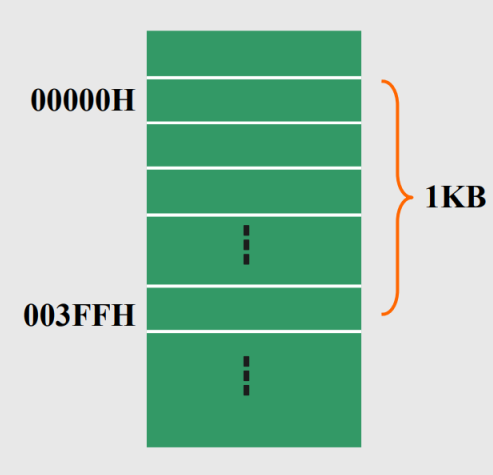

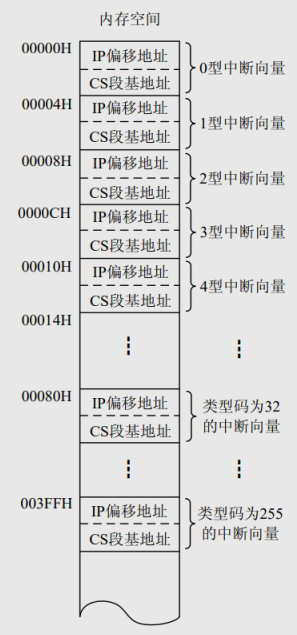

3.中断向量表

- 存放各类中断的中断服务程序的 入口地址;

- 位于内存的00000H~003FFH。

见图132

- 每个入口占用4 Bytes,低字为段内偏移,高字 为段基址;

- 中断向量表大小为1KB,共256个入口。

见图133

4.8088/8086中断系统

见图134

8088内部中断与NMI中断

- 特点:

- 无#INTA周期

- 中断类型码固定或指令给出

8088/8086 中断响应和处理流程

见图135

输入输出与中断技术小结

应理解:

- I/O接口的基本概念和功能

- 什么是/O端口?

- I/O端口的编址方式

- 4种基本I/O方法的特点及适用场合

- 什么是中断?什么是中断向量表?

- 中断响应的一般过程

应掌握:

- I/O接口译码电路设计方法

- 利用无条件传送或查询方式实现对简单外设的控制

- 利用三态门接口和锁存器接口芯片实现对简单外设的控制

注意点与常见问题

4种基本输入输出方法各自的应用场合

- 无条件传送方式:

- 外设随时处于“准备好”状态,且不能提供状态信息

- 查询方式:

- 外设必须要能够提供状态信息

- 中断方式:

- 外设必须具备发出高电平中断请求信号的能力

- 常用于实时性要求较高的中速外设控制

- DMA方式

- 整个输入输出由硬件系统完成,适用于高速外设。

- 无条件传送方式:

简单接口电路设计

- 译码电路设计

- 总线信号

接口系统的译码电路常采用部分地址译码

中断技术

- 中断响应的一般过程

- 中断向量表

- 每个表项的含义